P Koteswara rao\* et al. ISSN: 2250-3676

[IJESAT] [International Journal of Engineering Science & Advanced Technology] Volu

Volume-5, Issue-4, 444-449

# PROGRAMMABLE ARBITER FOR RUNTIME TRAFFIC PERMUTATION USING MULTI STAGE SWITCHING

P.Koteswara Rao<sup>1</sup>, Mande Srinivasa Rao<sup>2</sup>

<sup>1</sup>Asst.professor, ECE department, ALIET, JNTUK University, Vijayawada, A.P, India.

<sup>2</sup>Student, ECE department, ALIET, JNTUK University, Vijayawada, A.P, India. kotesh.iu@gmail.com<sup>1</sup>, mande438@gmail.com<sup>2</sup>

Abstract--- Multi processor system on chip (MPSoc) has been consider as the best candidate for applications such as networking, telecommunication, multimedia, medical etc. which have need of high computational demand, high performance, flexibility, high energy efficiency with robust architecture and low cost design in a minimum area. Multistage switching networks are best suited for applications which use large number of parallel systems and memories. MPsocs are well associated with switching networks to perform variety of scientific applications and parallel processing.

The proposed design presents a programmable and configurable arbiter in on chip networks adapted with MPsocs. The network used in design exploits a pipelined circuit switching scheme associated with dynamic path set up with multistage switching. This scheme is taken to provide guaranteed bandwidth for runtime traffic permutation and it provides dedicated path dynamically under multistage switching networks. The programmable arbiter can be used to increase efficiency of the system by programming with required arbitration schemes. The presence of a multiple scheme arbiter enables us to follow a scheme which is suitable for the application currently using the processor so that efficiency is increased.

*Index terms*: Multistage switching networks, Pipelined circuit switching, Dynamic path setup, Network on chip, MPSOCs, on chip network topology, Programmable Arbiter.

#### I. INTRODUCITON

Multiprocessor on-chip networks have risen in the past decade as an important class of VLSI family. A MPSoC is a on-chip system that combines most or all the components essential for an application that uses different programmable processors as system components. [1]. These designs are mainly used where we need high data transfer rates like telecommunication, signal processing etc. Most of the present trends are emerged with switching networks for multiprocessors. These are mainly used in scientific applications for parallel processing.

A multiprocessor system on chip is generally consists of different heterogeneous processing elements those may be distributed heterogeneously. Sometimes MPSoCs involves large amount of memory. Uniprocessors may not provide enough performance. These processors can handle limited number of PEs and small data. For real time applications multiprocessor Socs are compulsory to meet design constraints like power, area. MPSocs can reduce energy consumption and saves power. MPSocs are having so many challenges. Software development is the major challenge and this software should be in a position to gain enhanced performance. Each multiprocessor requires its own software development environment. There are different factors need to be considered for MPsocs like design methodologies and hardware architectures (which CPU is used, what processor is used and what interconnect and topology is used. Over the past decade various research attempts have encouraged primary enhancements. When formerly evolved systems embedded a single processor, the master of the chip, multiple masters must now share the overall control. The first Multiprocessors System on Chip (MPSocs) was developed. They combine several embedded processors, memories and specialized circuitry (accelerators, I/Os) interconnected through a dedicated framework to provide a complete integrated system. Converse to Socs, Mpsocs incorporate two or more main processors heading the application methodology, attaining higher productions[2].

The paper presents a novel design for proposed Guaranteed bandwidth arbitration algorithm for arbiter in multi stage switch circuit. The scheme offers better efficiency for the systems which involves large data rates at high speed .The scheme is proposed for multi stage MPSocs by overcoming drawbacks of previous arbitration schemes like Round robin and Fixed priority schemes. It also offers pipelined circuit switching with dynamic path setup for runtime traffic permutations.

The rest of this paper is organized as follows. Section II presents the Overview of multistage switching networks for MPSocs Section III gives the design approach for proposed design Section IV presents simulation results and analysis,

and finally, Section V concludes this paper and outlines the further researches.

### II. MULTI PROCESSOR SYSTEM ON CHIP WITH MULTISTAGE SWITCH CIRCUIT

Developments in semi conductor technology brought sensational changes in integrated circuit design by scaling down its size. The technology is kept on increasing from single chip, soc and multiple chips. But the services provided by this technology not sufficient because needs and demands are increased. The technology has grown and demands for applications also let the discovery of MPsocs and these has become a major class of VLSI technology. MPSocs have to serve with limited power applications with limited area. MPsocs must fulfil real time deadlines. Mpsocs generally designed with processing Elements, mini architectural blocks and interconnects with particular design parameters [5][11].

#### A.On chip network topology

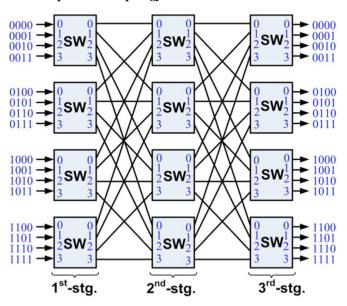

Fig.1.Proposed on-chip network topology with port addressing scheme

The on chip network topology belongs to clos network topology. It is used for commercial applications and it is best suit for MPsocs to support dynamic changes. It employs pipelining concept combined with dynamic path set up. The dynamic path-setup scheme enables arbitrary traffic permutations in run time. Because of dedicated path by circuit switching, data is guarantee reached to output. No data is missed. The circuit-switching approach offers a guarantee of

permuted data. The proposed design involves configuration and programming of Arbiter in switch circuit.

Clos network, also one of the important network topology families. It is more importantly used in MPsocs and each network consists of thousands of nodes. The figure shows a three-stage Clos network is named as f(p,q,r), where q represents the number of inputs in each of r first-stage switches and p is the number of second-stage switches. In order to support a parallelism degree of 16 as in most practical MPSoCs, we proposed to use f(4,4,4) as a topology for the designed network (see Fig 1). The peculiar behaviour of this topology is its rearrangeble property. Depends on our obligation we will lessen number of centre stages so that we reduce wiring costs there by implementation cost.

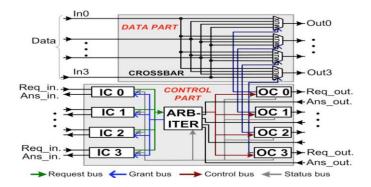

#### B. Common switch architecture and Programmable arbiter

These switches are all same as regular switch construction modelling shown in Fig.4.3. The difference between each switch is each one having different probing algorithms. The switch architecture has three main components: INPUT CONTROLs (ICs), OUTPUT CONTROLs (OCs), an ARBITER, and a CROSSBAR. To save the wiring costs Incoming probes are send through data paths. The ARBITER has two main functions:

- Connection of the Ans\_Outs and the ICs with the Grant bus,

- As a ref for the solicitations from the Ics.

Fig .2. Common switch architecture

The IC is used to cheque the output status through status bus when more than one incoming requests are reached at input and requests the ARBITER to connect to the requested OC through the Request bus. The ARBITER cross-connects the corresponding Ans\_Out with the IC through the Grant bus When accepting this request. The programmed ARBITER will

IJESAT | Jul-Aug 2015 445

apply its pre defined arbitration schemes and it solves the data conflict problem. When connection is happened only one output is selected, where as remaining routes are blocked.

#### **Programmable Arbiter**

In the previous design, the switch circuit consists of Arbiter as shown in above figure 2. This arbiter can be programmed and configurable with different arbitration schemes To overcome drawback in the previous system with arbitration schemes ,new design is proposed with new arbitration scheme for better efficiency. The previous schemes are itself are having drawbacks and these schemes are not suitable for all the real time applications.

## Proposed Arbitration scheme-Guaranteed Bandwidth (GBW) Scheme

In this scheme, all tasks or devices will get access those who put request for grant to communicate with other device. By overcoming drawbacks of above two schemes, means inefficiency in round robin, starvation problem in fixed priority, and this scheme provides better results so that the efficiency is increased

#### How this scheme works?

For example, four devices are trying for accessing or communicate with other device. All devices has put request for grant. we first initially assign priorities. Initially the highest priority device get access. what about other devices? Now the highest priority will get decreased by one value in next clock cycle or after getting first access. This process will continue until to the next highest priority value. Now the second highest priority device will get access. This process will continue to the next highest priority value and so on. In this all the devices will get access those devices put request for grant. So all the drawbacks are overcome and efficiency is increased.

#### IV.DESIGN FOR PROPOSED ARBITRATION SCHEME

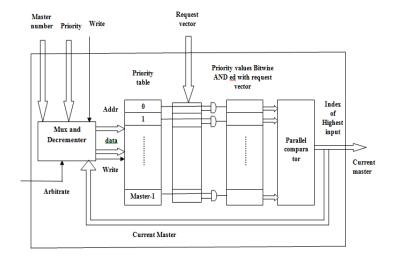

Fig 3 shows block diagram of proposed arbitration scheme. When arbitrate signal is high arbitration can be happened. Arbitrate signal is used to programming the all arbiters which are presented in the switch circuit and the current master priority value stored in corresponding address in priority table and also current master value decremented by one value. Master number and priority signals are inputs for Multiplexer. Write signal at input side of Multiplexer is used for programming masters with priorities and it is high while programming. The output write signal is used to write the data and address in priority table. Then the request vector and

priorities are logical ANDed bitwisely and the output is given to parallel comparator. The parallel comparator compares all values and gives highest priority signal as output. The actual output of parallel comparator is the priority value. Then only feedback from current master to the multiplexer is possible. The current master will always get access. In this way all devices will get grant to access the data. So that the throughput of system is increased.

Fig.3. Block Diagram for proposed arbitration scheme for Guaranteed Bandwidth Algorithm

#### V.SIMULATION RESULTS

In multistage switching networks there are several stages are involved in real time for traffic permutations. These permutations are dynamically changes as per availability of path for connection. Here the network employs a 3x4 on chip switch network topology, each stage having four switches and each switch having four inputs. Any device from input side can send data to any device from output side. For example, any of four devices are wants to communicate with same output at output side. For this we need put high request in signals. The output has to appear at required destination. Initially, arbiters are programmed with priorities for each device or input. In the simulation results, four devices or requests for same output at destination. As the proposed arbitration scheme, the data at four inputs reaches to required destination and each device gets access. So the efficiency is increased. Verilog HDL language is used for programming and ModelSim used for simulation.

446

P Koteswara rao\* et al. ISSN: 2250-3676

#### [IJESAT] [International Journal of Engineering Science & Advanced Technology] Volume-5, Issue-4, 444-449

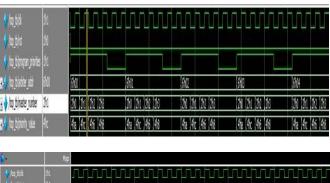

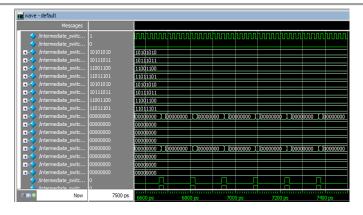

The proposed on chip topology is 3 stage switch circuit. At input side, four switches are present and each switch consists of 4 inputs. So total 16 inputs. To explain arbitration, for example 4 ports are requested for same output at destination. Since all ports are for same output address is same. Here it is written as 0\_0\_2. That means 0 th arbiter,0 th port in the 2<sup>nd</sup> stage. The output has to be reached to that address location. The below figures shows simulation results as follows. Fig 4 (a) arbiter programming with priorities Fig 4 (b) data at inputs Fig 4 (c) requests at input side Fig 4 (d) output at destination.

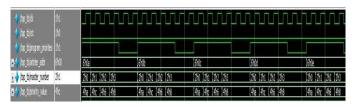

| / htp_tick<br>/ htp_ti/st                       | îil<br>110 | MM   |       |        | W |      | L    | 1    | VV  |      | mn |      | w   |     | M       |      | w.  |      |     |    |

|-------------------------------------------------|------------|------|-------|--------|---|------|------|------|-----|------|----|------|-----|-----|---------|------|-----|------|-----|----|

| // )to_b program_provides<br>// )to_b abble_add | ano<br>ano |      |       |        |   | 6h06 |      |      |     | 5h07 |    |      |     | (6h | 08      |      |     | 5h09 |     |    |

| top_b/naster_number                             | Zh1        | [2h0 | 211   | h2 (2h | 3 | Zh0  | [2h1 | 21/2 | 213 | 2h0  | 2  | 2h2  | 2h3 | (2) | 0   Zh  | 2/12 | 2h3 | 2h0  | 2h1 | 2h |

| 🅠 (top_tolpronity_value                         | fic        | 4ha  | fit f | h6 (4h |   | fha  | 4hc  | 46   | 48  | 4ha  | ٩c | (fhi | 418 | (4) | a   fho | 416  | 418 | 48   | Ac  | 4h |

Fig 4(a) Arbiters priorities programming

| /top_tb/in0_0 | 8hxx  | B'ha0 |   |    |

|---------------|-------|-------|---|----|

| /top_tb/in1_0 | 8"hxx | 8'ha4 |   |    |

| /top_tb/in2_0 | 8"hxx | 8'ha8 |   | 9  |

| /top_tb/in3_0 | 8"hxx | 8'hac |   |    |

| /top_tb/in0_1 | 8°hxx | 8'ha1 |   |    |

| /top_tb/in1_1 | 8"hxx | 8'ha5 |   | i. |

| /top_tb/in2_1 | 8'hxx | 8'ha9 |   |    |

| /top_tb/in3_1 | 8"hxx | 8'had |   |    |

| /top_tb/in0_2 | 8"hxx | 8'ha2 |   |    |

| /top_tb/in1_2 | 8"hxx | 8'ha6 |   |    |

| /top_tb/in2_2 | 8'hxx | 8'haa |   | Ş. |

| /top_tb/in3_2 | 8"hxx | 8'hae |   |    |

| /top_tb/in0_3 | 8°hxx | 8'ha3 |   |    |

| /top_tb/in1_3 | 8"hxx | 8'ha7 | 4 | ż  |

| /top_tb/in2_3 | 8"hxx | 8'hab |   |    |

| /top_tb/in3_3 | 8hxx  | B'haf |   |    |

Fig 4(b) data at input ports

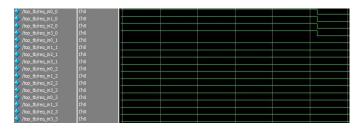

Fig 4(c) Single Stage Switch

Fig 4 (d) requests signals to the required destination

P Koteswara rao\* et al. ISSN: 2250-3676

#### [IJESAT] [International Journal of Engineering Science & Advanced Technology] Volume-5, Issue-4, 444-449

Fig 4(e) output at required destination port  $(0_0_2)$

#### **V.CONCLUSION**

To sustain heavy traffic permutation in multistage switch circuits, designers need to develop excellent methods at lower cost and limited area. The design uses a circuit-switching approach combined with dynamic path-setup scheme under a clos network topology. The proposed design offers a configurable and programmable arbiter with different arbitration schemes for arbitrary traffic permutation in runtime and the throughput is increased so that the efficiency of system also improved compared to the earlier design. With this design we can meet the present real time switching networks applications which involves high data rates.

#### REFERENCES

- [1] Wayne Wolf, Fellow, IEEE, Ahmed Amine Jerraya, and Grant Martin, Senior Member, IEEE, "Multiprocessor System-on-Chip (MPSoC) Technology" IEEE transactions on computer-aided design of integrated circuits and systems, vol. 27, no. 10, october 2008.

- [2] Lionel Torres, Pascal Benoit, Gilles Sassatelli, Michel Robert University Of Montpellier Lirmm Umr Cnrs, France Diego Puschini, Fabien Clermidy Cea-Leti, Grenoble, France, "An Introduction to Multi---Core System on Chip Trends and challenges"

- [3] Phi-Hung Pham, Junyoung Song, Jongsun Park, and Chulwoo Kim, "Design and Implementation of an On-Chip Permutation Network for Multiprocessor System-On-Chip" IEEE transactions on very large scale integration (VLSI) systems, vol. 21, no. 1, January 2013.

- [4] V.Prasanna Srinivasan, A.P.Shanthi, "A Survey Of Research And Practices In Multiprocessor System On Chip Design Space Exploration", Journal of Theoretical and Applied Information Technology, Vol. 64 No.1, 10 June 2014

- [5] Gianluca Palermo, Cristina Silvano, Vittorio Zaccaria Politecnico di Milano, An Efficient Design Space Exploration Methodology for Multiprocessor SoC Architectures based on Response Surface Methods", IEEE, 2008.

- [6] Shekhar Borkar, "Thousand Core Chips—A Technology Perspective", Intel Corp, Microprocessor Technology Lab, JF2-04, 2111 NE 25th Ave, Hillsboro, June 4-8, 2007.

- [7] Hazem Moussa, Olivier Muller, Amer Baghdadi, Michel Jézéquel, "Butterfly and Benes-Based on-Chip Communication Networks for Multiprocessor Turbo Decoding", 2007.

- [8] Phi-Hung Pham, Student Member, IEEE, Jongsun Park, Member, IEEE, Phuong Mau, and Chulwoo

- Kim, Senior Member, IEEE, "Design and Implementation of Backtracking Wave-Pipeline Switch to Support Guaranteed Throughput in Network-on-Chip", IEEE transactions on very large scale integration (VLSI) systems, vol. 20, no. 2, February 2012.

- [9] Geoffrey Blake, Ronald G. Dreslinski, and Trevor Mudge, "A Survey of Multicore Processors", IEEE Signal Processing Magazine, November 2009.

- [10] B. Neji, Y. Aydi , R. Ben-atitallah ,S. Meftaly , M. Abid , J-L. Dykeyser' "Multistage Interconnection Network for MPSoC: Performances study and prototyping on FPGA"

- [11] Sudeep pasricha, Nikil Dutt, "On-Chip Communication Architectures-system on chip interconnect, 2008.

- [12] Yuanyuan Yang, Senior Member, IEEE, and Jianchao Wang, Member, IEEE Computer Society, "A Fault-Tolerant Rearrange able Permutation Network, IEEE transactions on computers, vol. 53, no. 4, April 2004.

#### **AUTHOR:**

### [IJESAT] [International Journal of Engineering Science & Advanced Technology] Volume-5, Issue-4, 444-449

P.Koteswara Rao received M.Tech degree in Embedded system technology from SRM University, Chennai during 2008-2010.At present working as an Assistant professor in Andhra Loyola Institute of Engineering & Technology, ECE department, Vijayawada, A.P. India

M.Srinivasa Rao recived B.Tech degree in ECE from JNTUK university during 2008-2012.At present purcuing M.Tech inALIET in DECS branch,JNTUKUniversity,ECEdepartment,Vijayawad a,AP,India